Our Projects & Solutions

During passed 15 years, we have completed more than 50 projects.Here you can find the most significant:

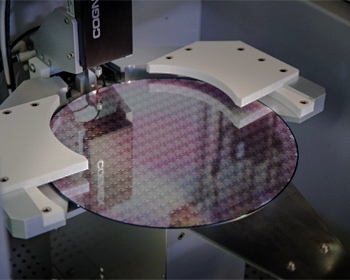

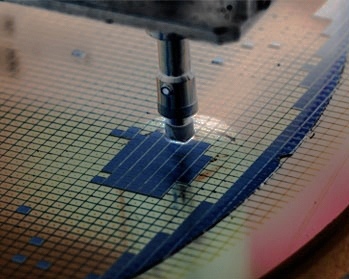

RTL Design & Verification Flow

Every project is unique, so we provide specific solutions for each of them

Working with Custom Chip Logic/IP Core/Verification IP in project we are not afraid of fresh ideas and original solutions

We always work together with the Partner and the Customer. Together we can overcome difficulties in the project. Is verification making troubles? Stuck with RTL design? We will help out

In addition to daily development practice, we usually improve our knowledge, make researches in field of our interests. We regularly visit seminars in fields of RTL design and Verification

Our developers are capable of SystemVerilog/Verilog/VHDL/С/С++/SystemC and use them actively developing our projects

We follow the Style Guides, always keep our code clear and reusable during development of each project

Greetings!

A team of experienced and talented engineers, graduated from National Research Nuclear University MEPhI. We are united by common goals and look for new knowledge and challenges.

Everyone in our team is specialist in digital curcitry and verification. Together we can solve wide range of tasks, but when project involves us into a new topic, we thoroughly immerse ourself into it.

Every new problem makes us more experienced. We have already successfully completed dozens of projects and participated in the development of modern SoC.

We won't stop developing and mastering modern technologies. Customers appreciate our energy and ambitiousness. We always help customers in creating their own innovative products. We generate intellectual property for them and implement their ideas.

Engineers that ready to help with Your projects

MSc: Department "Computer Systems and Technologies" MEPhI

Graduated in 2001

MSc: Department "Computer Systems and Technologies" MEPhI

Graduated in 2002

MSc: Department "Computer Systems and Technologies" MEPhI

Graduated in 2012

MSc: Department "Computer Systems and Technologies" MEPhI

Graduated in 2022

Master Student: Department "Computer Systems and Technologies" MEPhI

Graduation in 2023

Specialist: Department "Automatic control systems" BMTSU

Graduated in 2022

Bachelor Student: Department "Computer Systems and Technologies" MEPhI

Graduation in 2025

Bachelor Student: Department "Computer Systems and Technologies" MEPhI

Graduation in 2024

years of experience in

RTL Design & Verification

and more successful projects

partners

millon lines of working code

Any questions and suggestions are welcome.

In case the machines take over the World